Register merupakan sekelompok flip

flop yang dapat menyimpan informasi biner yang terdiri dari bit majemuk.

Register dengan n flip flop mampu menyimpan sebesar n bit data. Ada dua cara menyimpan dan membaca data ke dalam

register, yaitu seri dan paralel. Dalam operasi paralel, penyimpanan maupun

pembacaan dilakukan secara serentak oleh semua tingkat register. Sedangkan

untuk operasi seri, diterapkan secara sekuensial bit demi bit sampai semua

tingkat register terpenuhi.

Dalam praktek, untuk

mengisi register atau untuk menyimpan data dapat dilakukan dengan dua cara:

1. Dimasukkan secara Jajar (Parallel

In):

Pada cara ini semua bagian resgister atau

masing-masing flip-flop diisi (Loaded:dimuati) pada saat yang bersamaan. Atau

output masing-masing flip-flop akan respon sesuai data pada saat yang sama

setelah diberikan sinyal input kontrol.

2. Dimasukkan secara Deret (Serial

In):

Pada cara ini data dimasukkan bit demi bit

mulai dari flip-flop yang paling ujung (dapat dari kiri atau dari kanan), dan

digeser sampai semuanya terisi. Penggeseran data diatur oleh sinyal Clock tiap

kali data dimasukkan satu-persatu.

Cara yang pertama

(Parallel in) ditunjukkan sesuai gambar di bawah ini:

Prinsip-prinsip Kerja

Parallel In.

Ket: Ouput masing-masing

flip-flop akan respon sesuai data secara serempak setelah input control diberi

nilai logika “1”.

Output masing-masing

flip-flop akan respon sesuai data secara serempak setelah input kontrol diberi

nilai logika “1”.

Sedangkan pada cara

yang kedua (serial in), bila data digeser dari kanan ke kiri disebut “Register

bergeser ke kiri” (Shift-Left Register), sebaliknya bila data digeser dari kiri

ke kanan disebut “Register bergeser ke kanan” (Shift-Right Register).

Masing-masing cara tersebut digambarkan sesuai gambar di bawah ini:

Ket: Register dalam

keadaan kosong. Data siap masuk, menunggu Clock.

Dari prinsip kerja

Shift Register tersebut dapat dibangun satu macam register lagi yang dapat

bergeser ke kiri maupun ke kanan: Reversible Shift Register.

Memindahkan

data secara deret (serial transfer):

Pada gambar diatas data

dari register no.1(atas) dipindahkan ke register no.2(bawah) secara deret.

Dalam hal ini data akan keluar dari serial output register no.1 dan masuk ke

serial input no.2 berturut-turut atau bit demi bit. Pelaksanaannya diatur oleh

sinyal clock yang dihubungkan menjadi satu untuk kedua register tersebut. Pada

gambar diatas maasing-masing register bekerja bergeser ke kanan(Shift-right

register). Pada gambar di bawah ini dapat dilihat data yang berasal dari

register yang bergeser ke kanan dipindahkan ke register yang bergeser ke kiri.

Selanjutnya pada gambar serial output register

no.1 dihubungkan dengan serial input register no.2 dan serial output register

no.2 dihubungkan dengan serial input register no.1 . Pada kondisi ini data akan

bergeser secara berputar, dari register no.1 masuk ke register no.2 , kemudian

dari register no.2 kembali masuk ke register no.1 dan setersnya. Pengontrolan

dilakukan oleh sinyal clock, di mana karena masing-masing register hanya

terdiri dar empat flip-flop maka pada saat sinyal clock yang ke delapan data

akan kembali pada posisi semula.

MENYIMPAN DATA SECARA PARALLEL

Sebagaimana telah

diketahui, pada cara ini semua bagian Register atau masing-masing flip-flop

akan dimuati pada saat yang bersamaan (serempak). Hal itu diatur dengan suatu

sinyal pengontrol yang disebut Input control. Bila Input control =”0”, maka

semua flip-flop akan tetap stabil sesuai kondisi sebelumnya. Tetapi bila Input

Kontrol di ubah menjadi “1”, maka masing-masing data yang telah disiapkan untuk

disimpan akan masuk secara serempak. Untuk mengetahui cara kerjanya dapat dilihat gambar. Dimana

register dibangun dari empat buah D – Flip-Flop. (Dalam prakteknya dapat

digunakan J-K Flip-Flop).

Dimana:

Bila Input Kontrol =”0” input (Data) tidak mempengaruhi

output kedua tersebut.

Dalam keadaan input control “0” dapat di katakan bahwa pintu masuk

input di tutup data tidak di ijinkan masuk, sehingga output masing-masing

flip-flop tetap stabil sesuai kondisi sebelumnya.

Bila input control ”1” maka data input diijinkan masuk, sehingga

output masing-masing flip flop akan berubah sesuai dengan data yang ada pada

input.

Dan karena keempat flip-flop dari register gambar diatas dikontrol

oleh sinyal input control yang dihubungkan menjadi satu, maka mudah dimengerti

bahwa output masing-masing flip-flop tersebut akan merespon pada saat yang sama

(Serempak, ketika input control ”1” ).

MENGELUARKAN DATA SECARA PARALEL

Data yang telah

disimpan dalam Register dapat dikeluarkan atau “dibaca” pada saat yang

bersamaan. Hal ini diperlukan misalnya untuk sesuatu oprasi penjumlahan

bilangan atau untuk keperluan yang lainnya. Cara mengeluarkan data secara jajar

(serempak) dilakukan dengan menghubungkan masing-masing output flip-flop pada

gerbang AND, dimana salah satu input AND gate tersebut berfungsi sebagai tempat

jalan masuk sinyal pengontrolannya.

Dari gambar di atas dapat dilihat bahwa bila output control diberi

nilai “0”, maka output semua gerbnag AND adalah “0” tetapai bila output control

”1”, maka output Register akan dikeluarkan dan dapat dibaca pada saat yang

bersamaan. Dengan demikian penambahan AND gate pada rangkaian tersebut berguna

untuk mengatur kapan satnya data yang disimpan di Register tersebut akan

dikeluarkan untuk suatu keperluan tetentu. Dan data akan keluar dengan serempak

bila sinyal pengontrol atau output control ”1”.

MENYIMPAN DATA SECARA SERIAL

Seperti telah

disinggung pada permulaan bab ini menyimpan data secara Deret dilakukan dengan

memasukkan data (Yang berupa digit-digit bilangan Biner) bit demi bit mulai

flip-flop yang paling ujung, dan digeser satu per satu sampai semua flip-flop

terisi. Penggeseran data diatur oleh sinyal Clock.

Selanjutnya pada

gambar dibawah dapat dilihat rangkaian logika Register yang digunakan untuk

menyimpan data cara Deret (Shift Register). Rangkaian tersebut dibangun dari D

Flip-Flop yang berasal dari J,-K Flip-Flop, sehingga penggeseran data akan

berlangsung pada saat tepi naik.

Untuk membangun Register yang bergeser

ke kiri (Shift-Left Register), maka Serial Input Data dipasang mulai dari

flip-flop yang paling kanan (D), sedangkan outputnya dihubungkan dengan input

flip-flop C, demikian seterusnya tiap-tiap output flip-flop yang di sebelah

kanan dihubungkan dengan input flip-flop di sebelah kirinya.

Dari

gambar di atas yang lalu dapat dilihat bahwa output flip-flop yang paling kanan

diberi tanda Serial out, maksudnya adalah bahwa register tersebut dapat dibaca

atau dikeluarkan isinya secara deret. Data akan keluar secara Deret atau Bit

demi Bit dengan pengontrolan sinyal Clock. Dengan demikian data yang disimpan

secara Deret maupun secara Jajar dapat dikeluarkan dengan cara Deret. Juga,

bila diinginkan data yang disimpansecara Deret dapat dikeluarkan secara Jajar

dengan menggunakan AND Gate sesuai gambar di atas yang lalu.

Ada empat tipe

register yang dapat dirancang dengan kombinasi masukan dan keluaran dan

kombinasi serial atau paralel :

1.

Serial In Serial Out (SISO)

Pada register SISO,

jalur masuk data berjumlah satu dan jalur keluaran juga berjumlah satu. Pada

jenis register ini data mengalami pergeseran, flip flop pertama menerima

masukan dari input, sedangkan flip flop kedua menerima masukan dari flip flop

pertama dan seterusnya.

2.

Serial In Paralel Out (SIPO)

Register SIPO,

mempunyai satu saluran masukan saluran keluaran sejumlah flip flop yang

menyusunnya. Data masuk satu per satu (secara serial) dan dikeluarkan secara

serentak. Pengeluaran data dikendalikan oleh sebuah sinyal kontrol. Selama

sinyal kontrol tidak diberikan, data akan tetap tersimpan dalam register.

3.

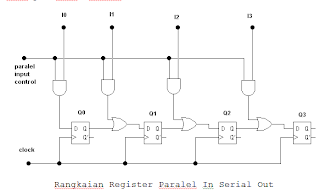

Paralel In serial Out (PISO)

Register PISO,

mempunyai jalur masukan sejumlah flip flop yang menyusunnya, dan hanya

mempunyai satu jalur keluaran. Data masuk ke dalam register secara serentak

dengan di kendalikan sinyal kontrol, sedangkan data keluar satu per satu

(secara serial).

4.

Paralel In Paralel Out (PIPO)

Register PIPO,

mempunyai jalur masukan dan keluaran sesuai dengan jumlah flip flop yang

menyusunnya. Pada jenis ini data masuk dan keluar secara serentak.

0 komentar:

Posting Komentar